Chapter 7

이번 시간에는 동기식 카운터를 설계하는 방법에 대해 배운다.

동기식 카운터를 설계하기 전 알아 둬야 할 상식

동기식 회로에서는 모든 FF가 하나의 CLK에 의해 제어된다.

- 하나의 동일한 클럭에 의해 모든 latch가 연결되어 제어될 때 그 회로를 동기식 회로라고 한다.

- 이번 시간에는 이렇게 하나의 클럭에 의해 counter 역할을 수행하는 회로를 설계해 볼 것이다.

동기식 카운터는 비동기식 카운터와 달리 전달지연이 없다.

- 비동기식 카운터의 회로는 아래와 같다.

- 비동기식 카운터는 단순히 위처럼 이전 FF의 output을 clk 입력으로 받아서 자신의 직전 digit이 1일 때 toggle된다.

- 이렇게 비동기식 카운터의 각 latch는 clk입력이 다 따로따로여서 전달지연이 생길 수밖에 없다. 이 지연이 쌓이고 쌓여 오류가 된다.

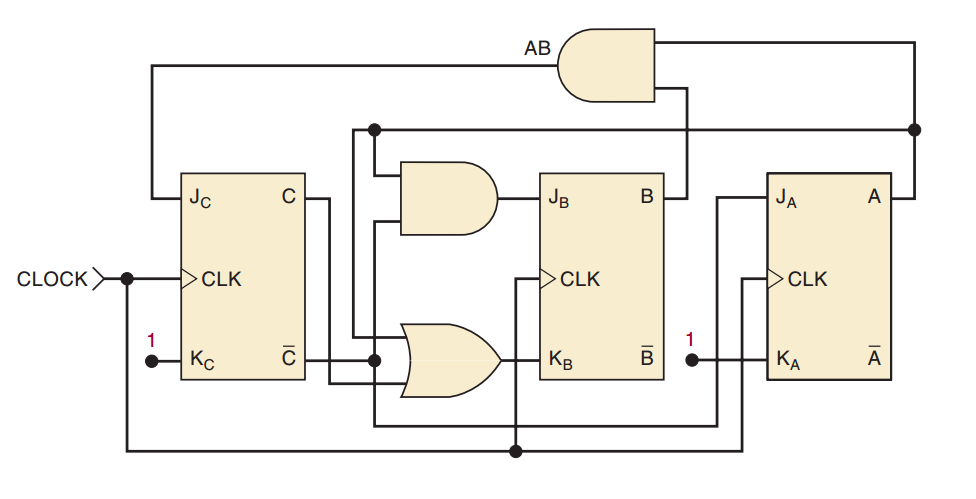

- 이 때 다음과 같이 동기식 카운터를 설계할 수 있다.

- CLK를 하나의 신호로 통일하고, 자신의 이전 digit들을 전부 AND한 값을 J, K입력으로 받아서 자신의 이전 digit들이 전부 1일 때 toggle되도록 한다.

- 이러한 동기식 카운터는 설계가 좀 더 복잡하지만 전달지연이 없다.

- 동기식이든 비동기식이든 counter의 동작은 다음과 같다.

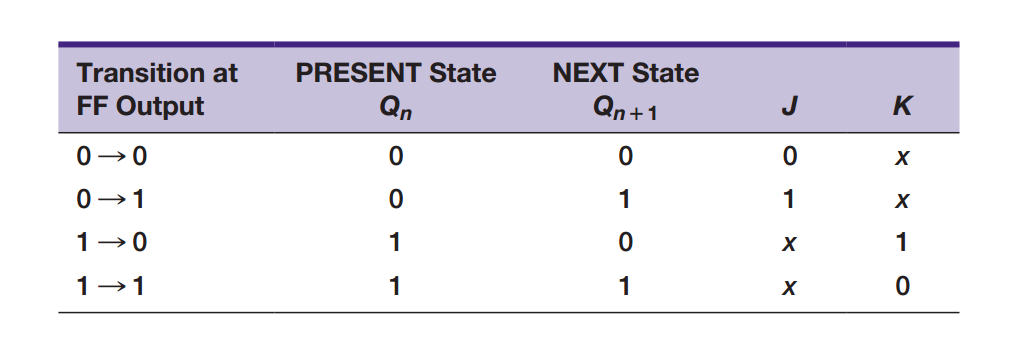

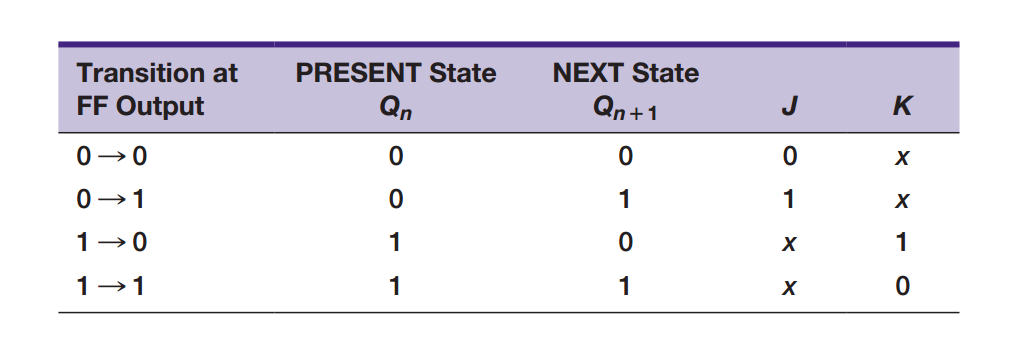

여기표(excitation table)는 FF의 output이 현재 상태에서 다음 상태로 가려면 input이 어떻게 되어야 하는지를 나타낸다.

- J-K FF의 여기표는 다음과 같다.

- 현 상태가 0일 때 0으로 만들려면, 가만히 있거나(J=0, K=0) reset 입력이 들어와야 하므로(J=0, K=1) K가 0이든 1이든 관계 없이 J=0이면 된다. 따라서 J=0, K=x.

- 현 상태가 0일 때 1로 만들려면, toggle되거나(J=1, K=1) set 입력이 들어와야 하므로(J=1, K=0) K가 0이든 1이든 관계 없이 J=1이면 된다. 따라서 J=1, K=x.

- 현 상태가 1일 때 0으로 만들려면, toggle되거나(J=1, K=1) reset 입력이 들어와야 하므로(J=0, K=1) J가 0이든 1이든 관계 없이 K=1이면 된다. 따라서 J=x, K=1.

- 현 상태가 1일 때 1로 만들려면, 가만히 있거나(J=0, K=0) set 입력이 들어와야 하므로(J=1, K=0) J가 0이든 1이든 관계 없이 K=0이면 된다. 따라서 J=x, K=0.

동기식 카운터 설계

동기식 카운터를 설계할 때는 5 step을 밟는다.

- 우리는 위에서 0000~1111 까지를 순차적으로 카운팅하는 카운터를 만들었다. 1111 다음엔 다시 0000으로 돌아가는 과정이 반복될 것이다.

- 이 때 만약 이렇게 순차적으로 흐르지 않고 0110, 1000, 1101, 0110...이 순차적으로 반복되는 카운터를 만들고 싶다면?

- 이렇게 원하는 흐름의 카운터를 직접 설계하는 방법을 배워보자.

동기식 카운터를 설계하는 5 step

000, 001, 010, 011, 100, 000...을 반복하는 카운터를 예시로 동기식 카운터를 설계해보자.

- 일단 하나의 digit 당 그걸 표현하는 Latch가 필요하므로 3개의 FF가 있어야 할 것이다.

- 2^3=8이므로 3개의 상태(101, 110, 111)는 사용되지 않을 것이다.

STEP 1: 원하는 수의 흐름을 쓰고 어떤 FF를 몇 개 쓸 지 정하기

- 000, 001, 010, 011, 100, 000... 을 반복하는 카운터를 만들고 싶다.

- JK latch를 쓸 것이다.

- digit이 3자리이므로 latch는 3개 쓸 것이다.

STEP 2: 상태 천이도 그리기

- 000, 001, 010, 011, 100, 000... 을 순차적으로 끝없이 반복한다.

- 원하지 않는 상태(010, 100, 111)는 전부 000으로 보낸다.

STEP 3: 각 현재 상태에 대한 다음 상태를 표로 그리기

- 현재 상태와 다음 상태 사이에 현재 상태를 다음 상태로 만드는 J, K 입력을 써 줄 거니까 사이를 크게 벌린다.

STEP 4: 각 latch에서 현재 출력을 다음 출력으로 만드는 J, K 입력 쓰기

- 위 표에서는 J, K 입력을 맨 오른쪽에 썼지만 실제로 설계할 때는 현재 상태와 다음 상태 사이에 집어넣는 게 편하다.

- 왜냐하면 이 표에서 현재 C, B, A 출력이 J, K 입력으로 들어가기 때문이다. J, K를 현재 상태 바로 옆에 때려 넣어야 평소에 하던 '왼쪽 입력, 오른쪽 출력' 의식의 흐름과 비슷해진다.

- 미리 J, K 여기표를 써놓고 그대로 베끼는 게 더 편하다.

STEP 5: 표를 기반으로 각 J, K에 대한 논리식을 구해서 최종 회로 그리기

- 위 표의 J(A)를 예로 들어서 논리식을 구해보자.

- 각 A, B, C가 입력으로 들어갈 때 J(A)의 출력 변화

- 해당 상태를 만드는 논리식 구하기. 일단 K-map을 그려보자.

- 딱 봤을 때 출력이 1이 되게 하는 경우의 input이 2개밖에 없다고 해서 K-map을 안 쓰고 넘어가는 건 근본없다. 위처럼 x들과 섞여서 더 간단해질 여지가 있기 때문이다.

- J(A)에 대한 논리식을 구했다. 이제 J(A), K(A), J(B), K(B), J(C), K(C)에 대한 논리식을 전부... 구한다...

- 다른 것들에 대한 K-map과 논리식을 구하면 다음과 같다.

- 위의 논리식들을 만족시키는 회로를 그린다. 이건 중간고사 범위.

노트 필기

'논리회로' 카테고리의 다른 글

| [논리회로] 기말고사 필기(플립플롭, 동기식 카운터 설계, verilog) (1) | 2022.12.09 |

|---|---|

| [논리회로] 4. 스탭모터 설계하기 (1) | 2022.11.27 |

| [논리회로] 2. digital pulse(펄스)와 clock(클럭) (0) | 2022.11.11 |

| [논리회로] 1. SR flip-flop (0) | 2022.11.11 |